International Journal of Advance Research in Science and Engineering Volume No. 11, Issue No. 06, June 2022 www.ijarse.com ISSN 2319 - 8354

# **COMPARISON OF DIFFERENT MULTIPLIERS BASED ON** THEIR PERFORMANCE PARAMETERS

Mrs. M. Poornima<sup>1</sup>, M. D. Nandhini<sup>2</sup>, M. Navaniswar Reddy<sup>3</sup>, M. Madhumitha<sup>4</sup>, P. Hemasimha<sup>5</sup>, P. Venkatesh<sup>6</sup>

<sup>1</sup>Assistant Professor, Dept. of ECE, S V College of Engineering, Tirupati, A.P, India.

<sup>23456</sup>B.Tech Students, Dept. of ECE, S V College of Engineering, Tirupati, A.P. India.

## ABSTRACT

Multiply and Accumulate (MAC) is the basic block that is used in each and every processor which consists of multiplier, adder and accumulator which in turn helps in increasing the speed of the complete processor. Its parameters such as LUT utilization and delay decides the performance of a DSP. So, there is a need to design area and delay efficient multiplier. A comparison is done between Vedic, Wallace, booth on comparing with various parameters like area, delay and speed. The best one is selected as per area, speed and delay constraints and that MAC is considered. The entire design is implemented in Verilog HDL. Synthesis and simulations were done using Xilinx ISE Design Suite 14.5. Here, we achieve significant improvement in area and delay.

Keywords: MAC, Vedic mathematics, look up table, Xilinx.

## 1. INTRODUCTION

In a "Digital Signal Processor" (DSP), the commonly used operations are "multiply and accumulate" (MAC), convolution and "Fast-Fourier Transforms" (FFT) etc. The multiplier is

considered as an essential block for the above operations. Power consumption in a DSP hugely depend on MAC unit. MAC unit consists of a multiplier, an adder for adding its partial products and an accumulator for storing the obtained results. So, for improving the speed of MAC unit, speed of the multiplier should be improved. MAC unit performs both multiply and addition functions. Its parameters such as LUT utilization and delay decides the performance of a DSP. As multiplication is termed as a widely used arithmetic operation, the research has always been aiming to design fast multipliers either by showing improvements in power, area or delay.

**IJARSE**

International Journal of Advance Research in Science and Engineering Volume No. 11, Issue No. 06, June 2022 www.ijarse.com

# 2. LITERATURE REVIEW

The Multiplier-accumulator (MAC) unit supports large number of digital signal processing (DSP) applications. Multiply and Accumulator assumes a significant part to choose the presentation of any DSP block. The better presentation of MAC unit satisfies the boundary of quick calculation and continuous handling abilities of a DSP. Multiply and accumulate is a basic block that is used in every processor which consists of multiplier, adder and accumulator. MAC unit performs both multiply and addition functions its parameters such as delay and area. In this paper, Vedic and Booth multipliers are the existing methods. To enhance the performance of the processor it is required to design a high speed, area and delay efficient multiplier i.e., Wallace multiplier. Referenced design is executed in Verilog HDL.

### **3. EXISTING METHOD**

Most of the DSP processors has MAC as its basic functional unit which performs complex multiplication and addition operations. Vedic multiplier and Booth multiplier has less delay and area. In a MAC unit multiplier are the essential block that determine the combinational path delay and area required to implement the hardware, so in this we need to design a high speed and area optimized multiplier i.e., Wallace multiplier.

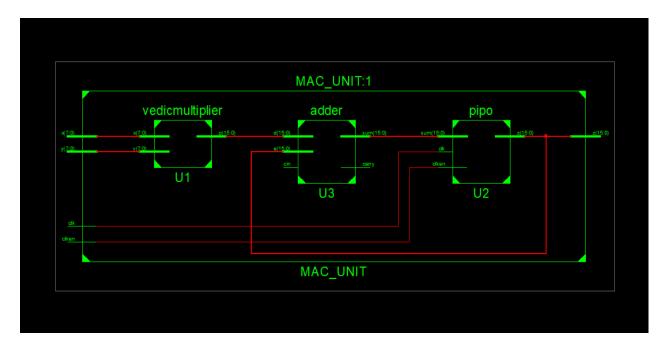

Figure 1: RTL Schematic for Vedic Multiplier based MAC

International Journal of Advance Research in Science and Engineering Volume No. 11, Issue No. 06, June 2022 IJARSE www.ijarse.com ISSN 2319 - 8354

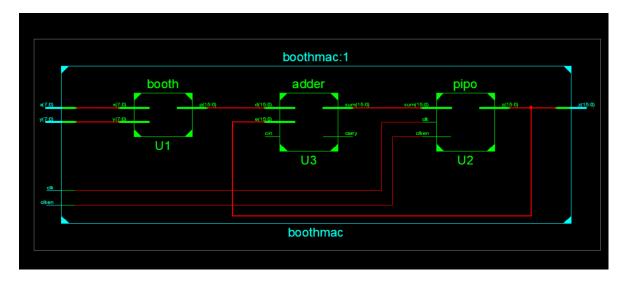

Figure 2: RTL Schematic for Booth Multiplier based MAC

## 4. PROPOSED METHOD

A comparison is done between Vedic, Booth, Wallace MAC's on comparing with various parameters like area, delay and speed. The best one is selected as per area, speed and delay constraints considered. The Synthesis and simulations were done using Xilinx ISE Design Suite 14.5.

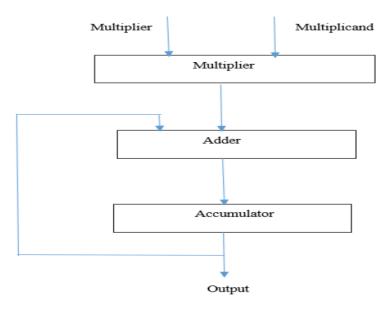

Figure 3: Block diagram of MAC

¢

International Journal of Advance Research in Science and Engineering

Volume No. 11, Issue No. 06, June 2022 www.ijarse.com

IJAKSE ISSN 2319 - 8354

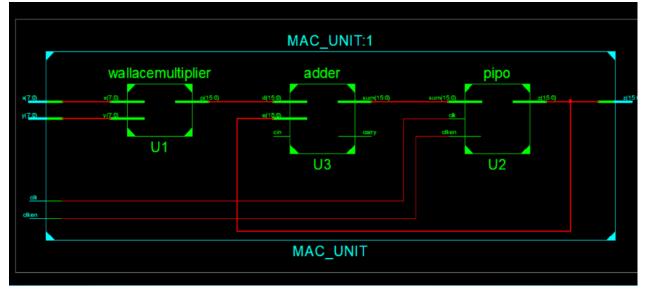

Figure 4: RTL Schematic for Wallace Multiplier based MAC

# 5. METHODS OR TECHNIQUES USED

The proposed Wallace multiplier is implemented in Verilog HDL stimulated in Xilinx ISE Design Suite 14.5. Verilog HDL is a hardware description language. It is a language used for describing a digital system like network system. It is very easy for designing and debugging.

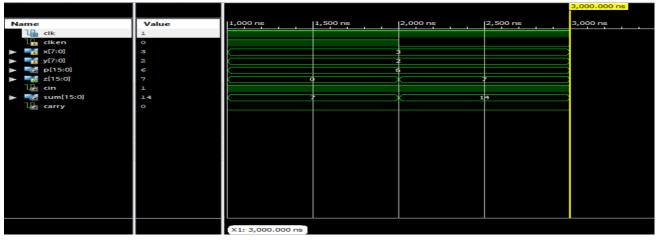

# 6. SIMULATION RESULT

From the analysis of all multipliers, wallace multiplier is the best multiplier. It has less area and less delay when compared to vedic and booth multipliers. This comparison helps us to select a suitable multiplier for a particular task or application.

Figure 5: Simulation result for Wallace Multiplier Based MAC

International Journal of Advance Research in Science and Engineering Volume No. 11, Issue No. 06, June 2022 www.ijarse.com ISSN 2319 - 8354

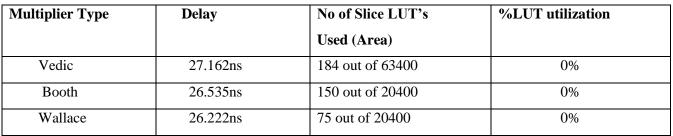

Table 1: Comparison of implemented Multipliers

#### 7. CONCLUSION

In this paper, three multipliers are compared with each other on basis of delay, area and speed. By comparing both existing and proposed multiplier, it is concluded that Wallace Multiplier has less delay and area when compared with the Vedic and booth Multiplier. In the existing system, the Vedic multiplier has a delay of 27.162ns and Booth multiplier has 26.535ns. In the proposed system, the Wallace multiplier has 26.222ns. On the study of above comparison, Wallace Multiplier has high speed and having lot of advantages.

#### 8. FUTURE SCOPE

For future research, a better multiplier can be proposed by modifying these multipliers and a better comparison of various multipliers with the proposed modified multiplier can be done by taking all multipliers simultaneously in one table. That will give more accurate comparison in percentage values.

#### 9. REFERENCES

- [1] G. Challa Ram, D. Sudha Rani, R. Balasaikesava, K. Bala Sindhuri, "Design of Delay Efficient Modified 16 bit Wallace Multiplier", IEEE International Conference On Recent Trends In Electronics Information Communication Technology, May 20-21, 2016, India.

- [2] Akella Srinivasa Krishna Vamsi and Ramesh S R, "An Efficient Design of 16 Bit MAC Unit using Vedic Mathematics", International Conference on Communication and Signal Processing, April 4-6, 2019, India.

- [3] D. Kalaiyarasi and M. Saraswathi, "Design of an Efficient High Speed Radix-4 Booth Multiplier for both Signed and Unsigned Numbers", 4th International Conference on Advances in Electrical, Electronics, Information, Communication and Bio-Informatics (AEEICB-18),2018.

**IJARSE**

# International Journal of Advance Research in Science and Engineering Volume No. 11, Issue No. 06, June 2022 www.ijarse.com

- [4] Jasbir Kaur, Sumit K, "Analysis and Comparison of Different Multiplier," International Journal on Recent and Innovation Trends in Computing and Communication ISSN: 2321-816975-78. Volume: 4 Issue: 6. June 2016.

- [5] Binta Lamba, Anurag Sharma, "A Review Paper on different multipliers based on their different performance parameters", Proceedings of the Second International Conference on Incentive Systems and Control (ICISC), 2018.

- [6] A. Eshack and S. Krishnakumar, "Implementation of Pipelined Low Power Multiplier", in 2nd International Conference on Trends in Electronics and Informatics (ICOEI), Tirunelveli, 2018, pp. 171-174.