# CASCADED SWITCHED-CAPACITOR MULTILEVEL INVERTER

Mammula Praveena Kumar<sup>1</sup>, A Anilkumar<sup>2</sup>

<sup>1</sup>PG student, Thandra Paparaya Institute of Science and Technology, Bobbili, AP. <sup>2</sup>Asst.Professor, Department Electrical and Electronics Engineering, Thandra Paparaya institute of science and technology, Bobbili, AP.

### Abstract

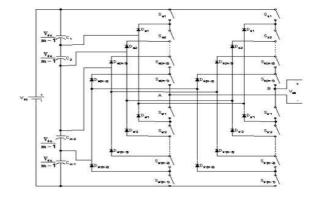

Proposed topology consists of a new switched-capacitor dc/dc converter (SCC) which has boost ability and can charge capacitors as self-balancing by using proposed binary asymmetrical algorithm and series-parallel conversion of power supply. Proposed SCC unit is used in new configuration as a sub-multilevel inverter (SMLI) and then, these proposed SMLIs are cascaded together and create a new cascaded multilevel inverter topology which is able to increase the number of output voltage levels remarkably without using any full H-bridge cell and also can pass the reverse current for inductive loads. Switched-capacitor multilevel inverters (SCMLIs) which can generate a great number of voltage levels with optimum number of components for both symmetric and asymmetric value of dc voltage sources. In this case, two half bridges modules besides two additional switches are employed in each of SMLI units instead of using a full H-bridge cell which contribute to reduce the number of involved components in the current path, value of blocked voltage, the variety of isolated dc voltage sources and as a result the overall cost by less number of switches in comparison with other presented topologies. The validity of the proposed SCMLI has been carried out by several simulation and experimental results.

Index Terms: Cascade sub-multilevel inverter, series parallel conversion, self-charge balancing, switched capacitor.

### 1. Introduction:

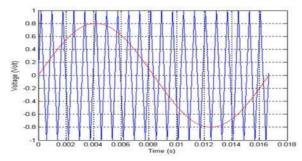

Electricity plays an important role in modern society since it was first used about one century ago. To utilize electricity for all kinds of tasks, many different electrical and electronic devices have been invented. Among these, the DC-AC converter is one of the most important power electronic devices. One of the most widely used strategies for controlling the AC output of power electronic converters is the technique known as pulse width modulation (PWM), which varies the duty cycle of the converter switches at a high switching frequency to achieve a target average low-frequency output voltage or current. A traditional sine-triangle PWM is shown in Figure 1.

Three significantly different PWM methods for determining the converter switching ON times have been usefully proposed for fixed-frequency modulation systems [1].

These PWM methods are:

- 1. Naturally sampled PWM: Switching at the intersection of a target reference waveform and a high-frequency carrier.

- 2. Regular sampled PWM: Switching at the intersection between a regularly sampled reference waveform and a high-frequency carrier.

Direct PWM: Switching so that the integrated area of the target reference waveform over the carrier interval is the same as the integrated area of the converter switch. Other PWM methods are variations of these three basic PWM methods. Even the well-known space vector modulation strategy, which is often claimed to be a completely different modulation approach, is really just a variation of regular sampled PWM which specifies the same switched pulse widths but places them a little differently in each carrier interval.

Figure 1: Sine-triangle PWM control sinusoidal reference signal and triangle carrier

signal

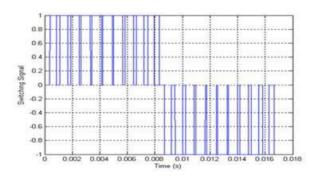

**Figure 2: switching signal**

#### 2. MULTILEVEL INVERTER:

Numerous industrial applications have begun to use high power apparatus in recent years. Some medium voltage motor drives and utility applications require medium voltage and megawatt power levels. For a medium voltage grid, it is troublesome to connect only one power semiconductor switch directly. As a result, a

multilevel inverter structure has been introduced as an alternative in medium and high power applications. With this type of inverters, improvements in the harmonic quality of the output voltage can be achieved. Multilevel inverter not only achieves high power ratings, but also enables the use of renewable energy sources. Renewable energy sources such as photovoltaic, wind and fuel cells can be easily interfaced to a multilevel inverter system for medium and high power applications. Multilevel inverter produces a desired AC voltage waveform from several levels of DC voltages. These DC voltages may be or may not be equal. AC voltage produced from these DC voltages is of stepped waveform. One drawback of using multilevel inverter is to approximate sinusoidal waveforms from stepped waveform. The staircase waveform produced by the multilevel inverter contains sharp transitions. Fourier series theory makes clear that this phenomenon results in harmonics, in addition to the fundamental frequency of the sinusoidal waveform. The power quality of the power system is affected by the harmonics generated on the AC side. The power quality of the multilevel inverter is improved by performing the power conversion in small voltage steps. Multilevel inverter widely replaces the conventional two level three phase Voltage Source Inverter (VSI) by its performance such as lower switching stress (dv/dt) and lower THD on output voltage. The multilevel inverters start from three levels. As the number of levels reach infinity, the output THD approaches zero. The number of the achievable voltage levels is limited by voltage unbalance problems, voltage clamping requirement, circuit layout and packaging constraints. A multilevel inverter has several advantages over a conventional two level inverter that uses high switching frequency PWM. The attractive features of a multilevel converter can be briefly summarized as follows:

- Multilevel inverters not only can generate the output voltages with very low distortion, but also can reduce the dv/dt stresses. Therefore, electromagnetic compatibility problems can be reduced.

- Multilevel inverters produce smaller CM voltage; Therefore, the stress in the bearings of a motor connected to a multilevel inverter drive can be reduced. Furthermore, CM voltage can be laminated by using advanced modulation techniques

- Multilevel inverters will draw input current with low distortion.

The main drawback of multilevel inverters is that the number of switches increases with the number of levels. In early stages of multilevel inverters, development of control circuitry for large number of power switches was a significant drawback of this inverter is the requirement of multiple numbers of DC voltage sources, mainly provided by capacitors. Balancing the voltage sources during operation under different load conditions is an important challenge. In spite of these drawbacks, introducing multilevel inverters will decrease switching losses occurred in the power device. By comparing with two level inverters, smaller size filter is required for the elimination of harmonics. This reduces the inverter weight, dimension and cost. Many multilevel inverter topologies have been proposed during the last two decades. Contemporary research has evolved novel inverter topologies and unique modulation schemes. MULTILEVEL inverters(MLIs) are known as one of the most popular solutions to improve the performance of renewable energy systems, electric vehicles (EVs) and other innovative power electronic utilities in medium and high power applications. These converters can generate a staircase voltage waveform at the output with high quality and desired spectrum. The desired output voltage is

synthesized by appropriate switching of several dc voltage links which leads to decrease voltage stresses on switches and total harmonic distortion (THD).

Here, the main and auxiliary power switches have to drive by fundamental and high switching frequency, respectively. Meanwhile, presented a triplen harmonic compensatory method based on fundamental switching strategy to extend the range of modulation index for three phase utility of 7-level CHB topology. Using the resonant switched capacitor circuit (RSCC) as an external voltage balancing network can also prevent this problem for DCMLIs. Nowadays, many researchers have presented numerous developed structures of MLIs with less number of key components such as number of required switches, gate drivers, power supplies and so on.

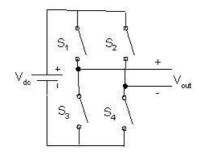

One of the most particular schemes of them is switched-capacitors multilevel inverters (SCMLIs). These converters can produce more output voltage levels with less number of required power supplies. SCMLIs contain several capacitors and switches which can connect dc power supply to ac output and are able to decrease the burden of power supply to achieve higher number voltage levels. Nevertheless, to attain the greater number of output voltage levels with less number of power semiconductors and simple commutation, a new type of SCMLIs have been emerged using the series/parallel switching strategy (SCISPC). The distinctive features of these types of inverters are that they can increase the flexibility of systems by switching between several capacitors in series or parallel modes and therefore can transfer more input power to the output. In this way, [9] and [10] presented a new family of cascade and hybrid SCISPC topologies which have a modular structure and generate more output voltage levels with least of switches. But such structures have used the full H-bridge units with isolated dc voltage sources to change the polarity of output voltage waveform which makes more conducting loss through the current path components and increases the number of power switches. Finally, validity of the proposed topology is shown by several experimental and simulation results.

#### **3.Diode-Clamped Converter:**

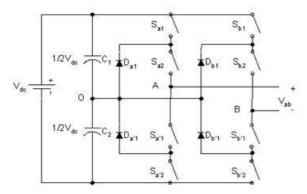

The simplest diode-clamped converter is commonly known as the neutral point clamped converter (NPC) which was introduced by Nabaeet al. [4]. The NPC consists of two pairs of series switches (upper and lower) in parallel with two series capacitors where the anode of the upper diode is connected to the midpoint (neutral) of the capacitors and its cathode to the midpoint of the upper pair of switches; the cathode of the lower diode is connected to the midpoint of the capacitors and divides the main DC voltage into smaller voltages, which is shown in Figure 2.1. In this example, the main DC voltage is divided into two. If the point O is taken as the ground reference, the three possible phase voltage outputs are  $-1/2V_{dc}$ .

The line-line voltages of two legs with the capacitors are:  $V_{dc}$ ,  $1/2V_{dc}$ , 0,  $-1/2V_{dc}$  or  $-V_{dc}$ . To generate a threephase voltage, three phases are necessary. The five-level output voltage can be generated by controlling the switches. Table 2-1 shows the proper switching states. The switches (S<sub>a1</sub> and S<sub>a'1</sub>) and (S<sub>a2</sub>and S<sub>a'2</sub>) are complementary pairs. When S<sub>a1</sub> is on (S<sub>a1</sub> = 1), S<sub>a'1</sub> is off (S<sub>a'1</sub> = 0). Other switch pairs are similar. Figure 2.2 shows a two-phase diode-clamped multilevel converter. Some disadvantages of the diode-clamped multilevel

converter may be observed. Using extra diodes in series becomes impractical when the number of levels m increases, requiring (m-1) (m-2) diodes per phase if all the diodes have equal blocking voltages. Note that the voltages for diodes in different positions are not balanced. For example, diode  $D_{a2}$  must block two capacitor voltages,  $D_{a(m-2)}$  must block (m-2) capacitor voltages. Also, the switch duty cycle is different for some of the switches requiring different current ratings. In addition, the capacitors do not share the same discharge or charge current resulting in a voltage imbalance of the series capacitors.

The capacitor voltage imbalance can be controlled by using a back-to-back topology, connecting resistors in parallel with capacitors, or using redundant voltage states [4].

The advantages for the diode-clamped converter are the following:

- (1) A large number of levels yields a small harmonic distortion.

- (2) All phases share the same DC bus.

- (3) Reactive power flow can be controlled.

- (4) Control is simple.

Figure 3: Neutral point diode-clamped converter converter

Figure 4: Two-phase diode-clamped multilevel

Table 1: Switch states and the output voltages for diode-clamped multilevel converter

| Sal | S <sub>a2</sub> | S <sub>a'1</sub> | S <sub>a'2</sub> | S <sub>b1</sub> | S <sub>b2</sub> | S <sub>b'1</sub> | Sb'2 | Vao                  | V <sub>bo</sub>      | V <sub>ab</sub>      |

|-----|-----------------|------------------|------------------|-----------------|-----------------|------------------|------|----------------------|----------------------|----------------------|

| 0   | 0               | 1                | 1                | 1               | 1               | 0                | 0    | -1/2 V <sub>dc</sub> | $1/2 V_{dc}$         | - V <sub>dc</sub>    |

| 0   | 0               | 1                | 1                | 0               | 1               | 1                | 0    | -1/2 V <sub>dc</sub> | 0                    | -1/2 V <sub>dc</sub> |

| 1   | 1               | 0                | 0                | 1               | 1               | 0                | 0    | 1/2 V <sub>dc</sub>  | 1/2 V <sub>dc</sub>  | 0                    |

| 0   | 0               | 1                | 1                | 0               | 0               | 1                | 1    | -1/2 V <sub>dc</sub> | -1/2 V <sub>dc</sub> | 0                    |

| 0   | 1               | 1                | 0                | 0               | 0               | 1                | 1    | 0                    | -1/2 V <sub>dc</sub> | $1/2 V_{dc}$         |

| 1   | 1               | 0                | 0                | 0               | 0               | 1                | 1    | 1/2 V <sub>dc</sub>  | -1/2 V <sub>dc</sub> | V <sub>dc</sub>      |

The disadvantages are the following:

- (1) Different voltage ratings for clamping diodes are required.

- (2) Real power flow is difficult because of the capacitors' imbalance.

(3) Different current ratings for switches are required due to their conduction duty cycle.

An output voltage can be produced by using different combinations of switches. The topology allows increased flexibility in how the majority of the voltagelevels may be chosen. In addition, the switches may be chosen to charge or discharge the clamped capacitors, which balance the capacitor voltage. The general m - level capacitor-clamped multilevel converter has an m-level output phase voltage. Thus, two phases would produce a (2m-1) level output voltage, or line voltage, which is shown in Figure 2.4. Similar to the diode-clamped multilevel converter, the capacitors have different ratings. These capacitors result in a bulky, and expensive converter when compared to the diode-clamped converter.bridge is shown in Figure 5. A single H-bridge is a three-level converter.

The advantages for cascaded multilevel H-bridge converter are the following:

- (1) The series structure allows a scalable, modularized circuit layout and packaging due to the identical structure of each H-bridge.

- (2) No extra clamping diodes or voltage balancing capacitors is necessary.

- (3) Switching redundancy for inner voltage levels is possible because the phase voltage is the sum of each bridge's output.

#### Figure 5: Two-phase capacitor-clamped multilevel converter

#### **5. CONCLUSION:**

In this paper, at the first, a new reduced components SCC topology was presented which has boost capability remarkably and also can pass the reverse current for inductive loads through existing power switches. The voltage of all capacitors in this structure is balanced by binary asymmetrical algorithm. Next, a new submultilevel structure based on suggested SCC was proposed which can generate all of the voltage levels at the output (even and odd). In this case, the conventional output H-bridge cell used to convert the polarity of SCC units, has been removed, therefore number of required IGBTs and other involved components, are decreased. After that, an optimizing operation was presented which could obvious the number of required capacitors in each of SCC units that participate in the cascade sub-multilevel inverter (CSMLI) to generate maximum number of output voltage levels with less number of elements. Moreover, comprehensive comparisons were given which prove the differences between improved symmetric and asymmetric CSMLIs in contrast to some of recently presented topologies in variety aspectsFinally, to confirm the performance and effectiveness of proposed

CSMLI, several simulation and experimental results have been presented.

#### REFERENCES

- Chaturvedi PK, Jain S, Agrawal P, Nema RK, Sao KK "Switching losses and harmonic investigations in multilevel inverters". IETE J Res 2008;54:297-307

- [2] B. Phani Chandra, K. Krishna Veni and Minakshi Khushoo "Investigations Of Harmonics And Switching Losses On Different Multilevel Inverter Control Techniques" By Simulation International J.of Multidispl. Research & Advcs. inEngg.(IJMRAE), ISSN 0975-7074, Vol. 2, No. III (October 2010), pp. 181-198

- [3] "Multilevel Power Converters" by SurinKhomfoi and Leon M. Tolbert, the University of Tennessee, a pdf.

- [4] K.H. Liu and F.C. Lee, "Zero-voltage switching technique in DC/DC converters", IEEE Trans. on Power Electronics, vol. 5, July 1990.

- [5] F. Canales, F, P. Barbosa and F.C. Lee, "A zero-voltage and zero-current switching three-level DC/DC converter", IEEE Trans. on Power Electronics, vol. 17, November 2002.

- [6] Werner Muth, "Matrix Method for Latch-up Free Demonstration in a Triple-Well Bulk- Silicon Technology", IEEE Trans. on Nuclear Science, vol 9, June 1992.

- [7] S. Voldmanet. al, "Latchup in merged triple well structure\_ Proceedings of reliability physics symposium", April 2005.

- [8] P. Gray, P. Hurst, S. Lewis and R. Meyer, "Analysis and design of analog integrated circuits", John Wiley & Sons Inc, 2001.

- [9] T. Tanzawa and T. Tanaka, "A dynamic analysis of the Dickson charge pump circuit", IEEE J. Solid-States Circuits, vol 32, August 1997.

- [10] J.T. Wu and K.L. Chang, "MOS Charge Pumps for Low-Voltage Operation", IEEE J. Solid-State Circuits, vol 33, April 1998.