International Journal of Advance Research in Science and Engineering

Vol. No.6, Issue No. 10, October 2017 www.ijarse.com

# **Implementation of ARM Processor using FPGA**

Shefa Parveen Butt<sup>1</sup>, Prof. Pravin Latane<sup>2</sup>

<sup>1,2</sup>ENTC Department, SIT Lonavala, Pune, Maharashtra, (India)

# ABSTRACT

Nowadays application specific fragile processor focuses are grabbing importance for FPGA based introduced application in which customer can plan the processor as indicated by need. The auxiliary straightforwardness of ARM processors makes them sensible for low power applications. Gear delineation lingos (HDLs) are for the most part used to create hardware structure. FPGA gives reconfigurable stage, so reuse of the layout is a regular practice to upgrade the productivity nowadays. In this paper the data taking care of rules of ARM processor areactualized using Very fast planned circuit Hardware Description Language (VHDL) vernacular and affirmed by applying test situate on Xilinx's Spartan III based FPGA.

Keywords- ARM, VHDL, FPGA, data processing instructions.

## I. INTRODUCTION

The Arm processor has far reaching uniform enroll record, stack/store plan, where data getting ready operations in a manner of speaking work on select substance, not clearly on memory substance. Clear keeping an eye on modes, with all load/store addresses being settled from enroll substance and rule fields simply Uniform and settled length course fields to revise rule decipher. The ARM processor has been especially planned to be little to diminish control usage and enlarge battery operation. The ARM configuration gives Control over both Arithmetic Logic Unit (ALU) and shifter in every data getting ready rule to enhance the use of an ALU and a shifter Load and Store various to help data throughput. These moves up to a central RISC building license ARM processors to fulfill a conventional change of prevalent, little code size and low power usage. The FPGA based arrangement reduces time to promote and incorporates design flexibility and adaptability with perfect device utilization and sparing both less load up space and system control, which is frequently not the possible for every circumstance of ASIC chips. In taking after this line of thought, this paper gathers our present progress in making VHDL sensitive focus of ARM processor sensitive fixate on FPGA is complete gear customization while realizing distinctive applications.

The paper is organized as follows: Introduction of the paper is in Section 1. Section 2 informs about the related work. Section 3 & 4 gives the detailing of the proposed work, its basic & result. Section 5 concludes the paper.

### **II. RELATED WORK**

The equipment troubleshooting innovation is coordinated in ARM processor with the goal that developers can see what is going on amid execution of code by processor. With this software engineers can resolve issues

# International Journal of Advance Research in Science and Engineering Vol. No.6, Issue No. 10, October 2017 www.ijarse.com

rapidly and decrease time to market and general advancement cost. The ARM is not unadulterated RISC design in light of different constraints of applications in installed framework. These days Speed is not real requirement but rather control utilization and financially savvyarrangements are likewise assuming crucial part. In ARM delicate processor center were executed with regards to FPGA based multiprocessor based SOC applications. All the 32-bit guidelines were actualized with single cycle information way and irregular rationale based direction decoder. The guidelines of Data preparing, Arithmetic, Branch directions, Logical and think about were executed. The proposed Virtual ARM Simulation Platform and examined how it can be utilized to decrease plan time and cost.

### **III. SYSTEM MODEL AND ASSUMPTIONS**

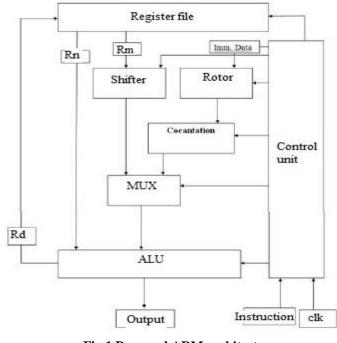

The ARM building has been expected to allow pretty much nothing and world class execution. The building ease of ARM processors prompts little executions, and little use allow devices with greatly low power use. The ARM is a decreased rule Set Computer (RISC), as it wires regular RISC building features. The proposed plan of the processor is showed up in Fig.1 The essential portions of the proposed configuration are

- 1. Enroll record which contains 16 enroll of 32 bits.

- 2. Barrel shifter of capacity to move 32 bit right/left, math/lucid.

- 3. Rotor having capacity to turn 8 bit data right/left.

- 4. Cocantation which change more than 8 bit yield of rotor into 32 bit.

- 5. Multiplexer which select one of two 32 bit inputs.

- 6. Calculating Logic Unit (ALU) to execute data getting ready rules

- 7. Control Unit which control all pieces as demonstrated by course.

Fig.1 Proposed ARM architecture

# International Journal of Advance Research in Science and Engineering Vol. No.6, Issue No. 10, October 2017 www.ijarse.com

#### **IV. IMPLEMENTATION & RESULT**

#### 1. Register file

It contains 16 enroll of 32 bits since we are using customer mode, all select are interested in customer. The component of enroll record and its entertainment result are showed up in fig.1.

2. Barrel shifter

The barrel shifter has a 32-bit commitment to be moved. This information is starting from the select archive. The shifter has other control inputs starting from control unit. Move field toward the path controls the operation of the barrel shifter. The fig.1 shows the substance depiction of barrel shifter.

The propagation eventual outcome of barrel shifter for number juggling left move operation is showed up in above fig.1

3. Control Unit

The control unit brings 32 bit heading and gives control signs to the distinctive the modules in the building. The controller give yields multiplexer controls, ALU limits, enroll scrutinizes/forms, pennants, move field, turn regard and other control signs to the gear depending upon the present rule. The substance and amusement result is showed up in fig.1

### V. CONCLUSION AND FUTURE SCOPE

The data planning bearings of ARM fragile focus processor were fused, duplicated and executed on Spartan III FPGA using Xilinx's ISE gadget. The code for each one of the modules were created using VHDL and attempted by applying test seats. Each one of the modules are working adequate as indicated by want. To the extent future work, there are various possible zones to improve and do encourage progression. So the ARM processor introduced into FPGA can be used for variousapplications like DSP and Image taking care of. The framework can be embedded into first class FPGA devices for better execution. The reconfigurable ARM focus can be used for affirmation organize in the undertakings.

# International Journal of Advance Research in Science and Engineering

Vol. No.6, Issue No. 10, October 2017 www.ijarse.com

### REFERENCES

- Y B T Sundari, T. Surender Reddy, Dr. Laxminarayana G, "Implementing the ARM7 soft core processor in FPGA", IJCER, vol.2, pp 153-159Apr. 2013.

- [2] Alex Heunhe Han, Young-Si Hwang, Young Ho An, So-Jin Lee, Ki-Seok Chung, "Virtual ARM Platform for Embedded SystemDevelopers", IEEE 2008 pp586-592

- [3] J. O. Hamblen, T. S. Hall, "Using System-on Programmable-Chip Technology to Design Embedded System", IJCA, Vol. 13, No. 3, pp 1-11, Sept. 2006.

- [4] Goslin, G. R. "A Guide to Using Field Programmable Gate Arrays (FPGAs) for application Specific Digital Signal Processing Performance", Xilinx Application Note, 1995.

[5] ARM Architecture Reference Manual.