Volume No. 11, Issue No. 06, June 2022 www.ijarse.com

# DESIGN AND IMPLEMENTATION OF A DUAL SLOPE ADC

# D. Chaitanya<sup>1</sup>, K Ramya Sree<sup>2</sup>, Galla Bhavana<sup>3</sup>, Poojari Yamini Devi K Rohith<sup>4</sup>, Kollu Bhanukarthik<sup>5</sup>, Kola Sai Charan<sup>6</sup>

<sup>1</sup>Assitant Professor, Dept. of ECE, S V College of Engineering, Tirupati, A.P, India. <sup>23456</sup>UG students, Dept. of ECE, S V College of Engineering, Tirupati, A.P, India.

#### **ABSTRACT**

Analog-to-digital converter (ADC) is most commonly used in nearly all kinds of electronics. In real world, signals such as voice, image and other information are analog, but in electronic devices, only digital signals can be processed, which means all analog signals needs to be converted into digital signals. An ADC is supposed to complete such conversions. It converts the analog signals (voltages, currents and etc.) into digital signals (normally binary), which will be processed by a DSP in electronic devices. On the other hand, a digital-to-analog converter (DAC) performs the opposite way.

In this project work an 8-bit Dual Slope ADC using two cascaded 4-bit counters is designed and implemented. The design of Dual Slope ADC was first done by creating the various parts of operation in pieces to check they function before finally putting them all together. This design was done with the help of MULTISM simulation tool where all the design was made. Various simulations are carried out to check for errors and it efficiency. Comparison table and necessary graphs related to the operating speed, power consumption and number of bits will be drawn in this project work.

**Keywords:** Metal Oxide Field Effect Transistor, Analog to Digital converter, Digital to Analog converter, Signal to Noise Ratio, Root Mean Square, Operational Amplifier.

#### 1. INTRODUCTION

We live in an analog world, surrounded by digital devices. Everything we see, feel or measure is analog in nature such as light, temperature, speed, pressure etc. But most of the electronic devices around us starting from a simple digital watch to a super computer are all digital devices. So, it is obvious that we need something that could convert these analog parameters to digital value for a microcontroller or microprocessor to understand it. This something is called the ADC or Analog to Digital Converter and in this ADC article we will learn more about them.

Consider a temperature monitoring system wherein acquiring, analyzing, and processing temperature data from sensors is not possible with digital computers and processors. Therefore, this

Volume No. 11, Issue No. 06, June 2022 www.ijarse.com

system needs an intermediate device to convert the analog temperature data into digital data in order to communicate with digital processors like microcontrollers and microprocessors. Analog to Digital Converter (ADC) is an electronic integrated circuit used to convert the analog signals such as voltages to digital or binary form consisting of 1s and 0s.

In this paper implementation of dual slope ADC is introduced which designed by using a comparator, integrator, switch and the cascaded counter. The increasing the accuracy converter and with the help of the capacitor which charges and discharges to set the rise and fall of the voltage level which drives the counter.

#### 2. LITERATURE REVIEW OF DUAL SLOPE ADC

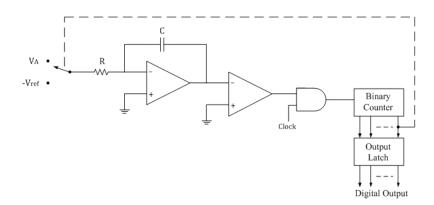

In dual slope type ADC, the integrator generates two different ramps, one with the known analog input voltage VA and another with a known reference voltage –Vref. Hence it is called a s dual slope A to D converter. The logic diagram for the same is shown below.

Figure 1: Block diagram of dual-slope ADC

In order to understand the architecture of Dual slope ADC we first need to understand the concept of single slope ADC. The single slope ADC is also known as integrating ADC and the main theme of this architecture is to use analog ramping circuit and digital counter instead of using DAC. The op-amp circuit that is also called an integrator is used to generate a reference ramp signal that will compare with input signal by a comparator. The digital counter clocked with precise frequency is used to measure time taken by the reference signal to exceed the input signal voltage. The Dual-Slope ADC input voltage (VIN)

Volume No. 11, Issue No. 06, June 2022 www.ijarse.com

integrates for fixed time interval (TINT), then it will be integrated by using reference voltage (REFV) for a variable amount of time (TDE-INT).

#### 3. EXISTING METHOD

#### **Dual slope ADC:**

The input voltage signal is used to charge the capacitor so that its voltage reaches a fixed threshold. Then the digitally created circuit measures the time needed to reach its threshold by means of counting the pulses generated from a fixed-frequency clock. This type of conversion can be used often where there is the need for high resolution but slow, low-precision converters because very little components are required. It has two major parts: first, the circuit which digitalizes the acquired input thereby producing a pulse phase sequence and the other, the counter(N-bit) which converts the result into a digital value.

The working process requires the use of the input voltage to charge the capacitor for a fixed time period. The capacitor's reference voltage discharges the capacitor and the digital control circuit measures the time for the capacitor to discharge completely. The ratio of the discharge time to the charging time is the ratio of the unknown to the known voltage. This conversion type operates independently of its integrator component's values, due to the fact that charging and discharging is done by the same circuit.

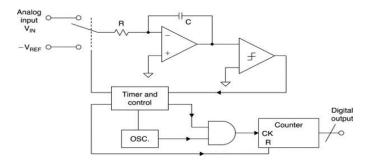

The Dual slope ADC circuit, is made up of a switch, an integrator, a timer showing the needed time when the unknown voltage is integrated the unknown and measures the reference voltage timing as well as the controller, and a comparator. The switch should be placed between the voltage measured and the reference voltage (negative). Based on the kind of operation, resetting the integrator, thus by discharging is done by a parallel connection of the integrator capacitor.

Figure 2: Dual Slope ADC

Volume No. 11, Issue No. 06, June 2022 www.ijarse.com

Figure 3: Dual slope conversion cycle

This Dual slope conversion has two phases; the run-up also referred to as the 'counting up' phase and the run-down phase(counting down). During run-up, the voltage supplied to the integrator is measured. At which point, the input voltage provided to the integrator which is selected by the switch is measured. The integrator is then allowed to ramp for a fixed interval of time for the charging of the capacitor. For the run-down phase, an input to the integrator is in the form of a negative reference voltage, the switch then chooses this reference voltage to be its input voltage of the integrator. The time taken for the integrator's output to return to zero value is measured during this phase.

#### 4. PROPOSED METHOD

#### **Dual slope ADC:**

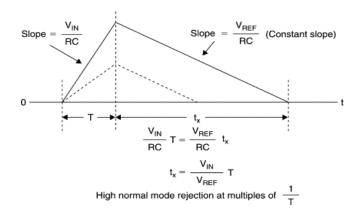

A Dual slope ADC with high speed compared to existing system and good accuracy, which will be helpful for designing effective voltmeters. High speed switches and high-speed operational amplifier is used in this design.

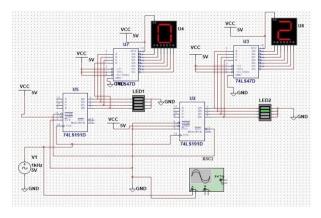

Figure 4: Dual Slope ADC Design in Multisim

Volume No. 11, Issue No. 06, June 2022 www.ijarse.com

Figure 5: Proposed Dual Slope ADC Integrated Circuit

## 5. METHODS OR TECHNIQUES USED

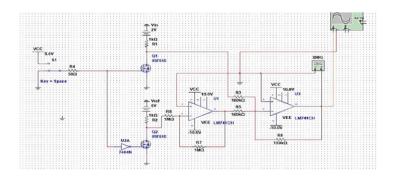

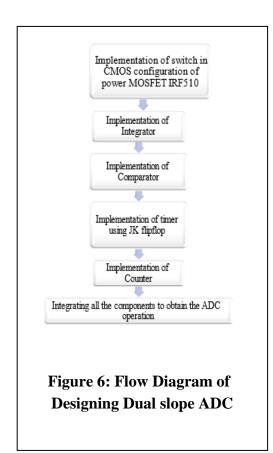

To Design the Dual slope Integrating Type ADC, we have categorized the whole circuit into two blocks i.e., analog and digital part and further sub divided the analog circuit into smaller circuit components like integrator, switch, comparator and digital circuit into smaller circuit components like counter, JK flipflop etc. and implemented in MULTSIM and simulation results were taken, to understand working of each block and also to have idea on where we can improve the performance of ADC.

Figure 7: Methodology

Volume No. 11, Issue No. 06, June 2022 www.ijarse.com

## 6. RESULT

| PARAMETERS                             | VALUES                       |

|----------------------------------------|------------------------------|

| Number of Bits that ADC can Convert to | 8 bits                       |

| Clock Frequency                        | 1MHz(I MegaHertz)            |

| Clock Time Period                      | 1us(1 Micro Second)          |

| Conversion time for integrating Va     | 255us                        |

| Conversion Time for integrating Vr     | 255us                        |

| Total conversion time for whole ADC    | 510us                        |

| Components used                        | IRF510 MOSFET,LM741CH OPAMP, |

|                                        | 74LS191D 4 BIT COUNTER,7404N |

|                                        | INVERTER                     |

| Applied Input Analog Voltage           | 2V                           |

| Applied Reference Voltage              | 5V                           |

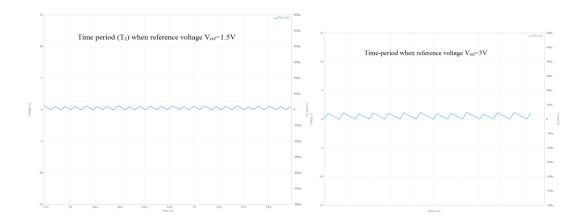

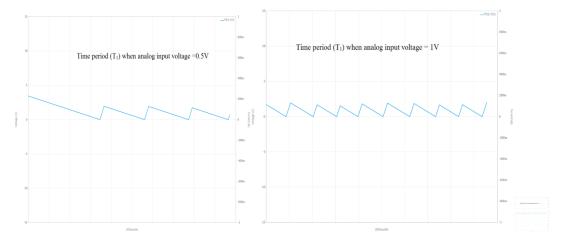

In order to obtain the less conversion speed, the time taken for discharging (T2) must be very much smaller.so from the relation

$$Vin = -Vref * (T2/T1)$$

So to reduce the value of T2, the reference voltage has to be increased as Vref is inversely related to T2.

Volume No. 11, Issue No. 06, June 2022 www.ijarse.com

Thus by reducing the reference voltage and increasing the input analog voltage, the conversion time can be reduced.

#### 7. CONCLUSION

The main goal of the thesis was to create and study the operations of a Dual slope ADC with a 8 Bit counter (cascaded 4 Bit counter) and compare the one obtained from the study to the theoretical aspect of that ADC model. With this design model, a comparator, integrator, switch and the cascaded counter was the major equipment required to achieved this goal.

Though, after carefully calculating the adequate values for the Resistance and capacitor needed most especially for the integrator, the actual value was not available in the Laboratory but a similar or one closer to the value was used as a replacement for the setup.

The simulation of the final work was done with the aid of Multisim, which gave a good response to the waveform expected as to that of the theory.

After the experiment, it can be concluded that a vivid and thorough work was done to verify the Dual slope ADC operations, which with the help of the capacitor which charges and discharges to set the rise and fall of the voltage level which drives the counter.

#### **8.FUTURESCOPE**

In Future, there is scope for an area efficient, low power consumption and reducing the size of the circuit and making it more compatible. And implementing idea of dual slope ADC in advance tools.

Volume No. 11, Issue No. 06, June 2022 www.ijarse.com

#### 9. REFERENCES

- 1. Kleitz, W., 2006. Digital Electronics with VHDL. Quartus II Version, Prentice Hall, ISBN: 0-13-171490-2.

- Kyung, C.M. and C.K. Kim, 1981. Charge-coupled analog-to-digital converter. IEEE J. Solid-State Circ., 16:621-626.

http://ieeexplore.ieee.org/xpl/freeabs\_all.jsp?tp=&a renumbers=1051653&isnumber=22580

- Sasaki, K. and N. Yoshida, 2003. Analog to digital conversion taking into account speed of signal change and its accuracy. Proceeding of the SICE Annual Conference, Aug. 4-6, IEE Explore Press, Fukui, pp:380-385.

DOI: 10.1109/SICE.2003.1323376

- 4. Quevedo, D.E. and G.C. Goodwin, 2005. Multistep optimal analog-to-digital conversion. IEEE Trans. Circ. Syst., 52: 503-515. DOI: 10.1109/TCSI.2004.843058

- 5. Powell, I.A. and W.J. Perold, 2007. A switching logic digitizer for analog-to-digital conversion.

- 6. Bou Hedda, M., M. Attari and B. Granado, 2007. FPGA implementation of nural nonlinear ADC-based temperature measurement system. Proceeding of the IEEE International Workshop on Intelligent Data Acquisition and Advanced Computing Systems:

- 7. Technology and Applications, Dortmund, Germany, Sept. 6-8, IEEE Xplore Press, Dortmund, pp: 232-237. DOI: 10.1109/IDAACS.2007.4488411

- 7 Tocci, R.J., N.S. Widmer and G.L. Moss, 2004. Digital Systems: Principles and Applications. 9th Edn., Prentice Hall, ISBN: 0-13-111120-5.

- 8. Bartee, T.C., 1991. Computer Architecture and Logic Design. McGraw Hill, ISBN: 0-07-003909-7, pp: 628.

- 9. Shiva, S.G., 1991. Computer Design and Architecture. 2nd Edn., Harper Collins, ISBN: 0-673 39683-5, pp: 594.

- 10. Texas Instruments Incorporated, 1985. The TTL Data Book-Standard TTL. Schottky, Low-Power Schottky Circuits, Vol. 2, ISBN: 0-89512-096-8, 1985.