# **Analog Signal Processing Applications of Current Mirror Amplifier: A circuit design perspective**

Kamini<sup>1</sup>, M. Y. Yasin<sup>2</sup>

<sup>1</sup>Research Scholar, Electronics Communication Engineering Department, Integral university, Lucknow, (India).

<sup>2</sup>Faculty, Electronics Communication Engineering Department, Integral university, Lucknow, (India)

#### **Abstract**

Analog design can be considered as design procedure which fall underboth the voltage-mode and the current-mode form of signal processing. A new approach of current amplifier, integrator, differentiator and low pass filter design using CM (current mirror) is presented in this work, all the proposed circuits were tested in HSPICE (Hewlett Simulation Program with Integrated Circuit Emphasis) using 45nm CMOS (Complementary metal oxide semiconductor) technology and it is found that the obtained results are according to their theoretical values. The proposed circuits are employing the NMOS (n-type metal oxide semiconductor) CM and these circuits can be considered as a LVLP (low voltage and low power). The analog circuits along with the proposed topologies are very attractive because of their simple structure and easy implementation of operations. The current mirror circuits fulfil the requirements of a modern low-power wireless and biomedical applications such as complex filters for Bluetooth low-IF (intermediate frequency) receivers and Wavelet filters for cardiac signal detection etc.

Keywords: Current mirror, current amplifier, Current mirror integrator, Current mirror differentiator, Current mirror low pass filter, Current mirror filter.

#### 1. Introduction

The current mirror circuit has served as basic building block in current mode Analog circuit design. Current mirror circuit plays an important role to decide the overall circuit characteristics. Now days integrated circuit industry concentrating on developing devices which employing the following properties like low-voltage operation, low power consumption, wide bandwidth and minimum area requirement, therefore there is extreme need for low-voltage Analog circuit designs [1-3]. The current mirror is a two terminal device, as its name implies it is having a property to copy the input current at the output terminal, and the output current is independent on output terminal voltage and depends only on the input current [5-8]. In this paper, the analysis of basic and scaled version of the current mirror is presented and also their suitable involvement into the designing and fabrication of LVLP analog circuits like integrator, differentiator and low pass filter designing is verified with the help of HSPICE tool based on 45nm CMOS technology.

# 2. Methodology

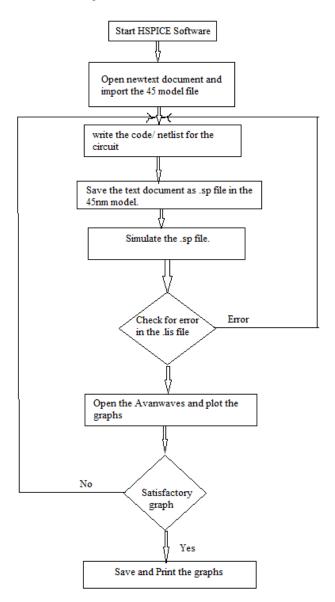

The different circuits have been designed using current mirror. The HSPICEsoftware is used to simulate the circuit performances. The CMOS 45nm technology has been used to import the model file in HSPICE. The typical process to simulate the current amplifier, integrator, differentiator and low pass filter has been explained through flow chart shown in figure 1.

Figure 1.Flow chart of simulation process in HSPICE Software [9].

# 3. Circuit description

### 3.1The Simple Current Mirror

A current mirror is used to copy or multiply the input current. It is often used as a bias circuit that provides a known current to an Analog circuit like a common-source amplifier with an active load. A simple NMOS current mirror is shown in Figure. 3.1. It comprises two NMOS transistors M1 and M2, one of which has the base and drain connected and the other does not, assuming that M1 and M2 have same width and length and  $V_{GS1} = V_{DS1} = V_{GS2} = V_{DS2}$ . Because the MOSFETs have the same gate-source voltages, it is expected them to have same drain current. Neglecting channel length modulation, the currents relations can be expressed as

$$I_{\text{ref}} = \left(\frac{1}{2}\right) \mu_{\text{n}} C_{\text{ox}} (W|L)_{1} (V_{\text{gs}} - V_{\text{th}})^{2}$$

(3.1)

$$I_{out} = {}_{n} C_{ox} {}_{2} (V_{gs} - V_{th})^{2} (3.2)$$

Figure 3.1Simple NMOS current mirror.

### 3.2 Scaled Current Mirror

The applied input current is source to a first current turn around circuit for sinking a current at a terminal thereof substantially equal to the input current. A current mirror provides an output current that is scaled in magnitude with respect to an applied input current includes first and second current turnaround circuits and circuitry coupled between the two current turnaround circuits which is responsive to the first current

turnaround circuit for sourcing a current to the second current turnaround circuit the magnitude of which is scaled with respect to the input current that is sourced to the first current turn around circuit. By dividing the equation (3.2) by equation (3.1), we get the equation (3.3)

$$\frac{\text{Iout}}{\text{Iref}} = \frac{(w|L)2}{(w|L)1}(3.3)$$

typically,the lengths of the device in the current mirror are equal, and at the same time if channel length modulation is neglected ( $\lambda = 0$ ), the output gain will be reflected as equation (3.4).

$$\frac{\text{lout}}{\text{Iref}} = \frac{\text{W2}}{\text{W1}}(3.4)$$

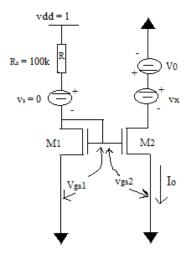

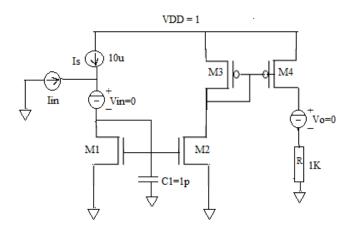

Figure 3.2Current amplifier using CM.

By simply changing the width and length of the another transistor the output current can be scaled up or scaled down. Using this property of current mirror, current amplifier circuit is designed, by using two NMOS transistors M1(w=45, l=45) and M2(w=90, l=45) of different parameters and a resistance  $R_s$  of 100kohm. The output current can be seen across Vo, which is a pseudo voltage of 0V. The proposed circuit is shown in figure 3.2.

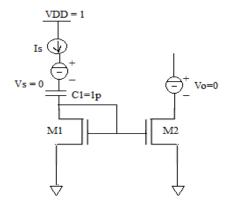

### 3.3 Current mirror Integrator

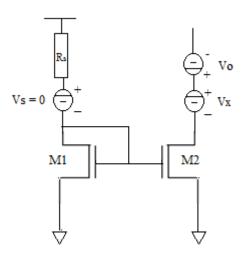

The integrator circuit is proposed using NMOS current mirror as shown in the fig 3.3 and the given circuit is composed of a NMOS current mirror. In the designing of integrator circuit, it is assumed that (W/L) ratio of both the transistors are kept equal with a capacitor connected at the gate terminal of both NMOS transistors. This circuit produces the similar response as of passive integrator but at a very low voltage of 1v. Which can be seen across the pseudo terminal voltage Vo of 0V.

# International Journal of Advance Research in Science and Engineering Volume No.08, Issue No.07, July 2019

# www.ijarse.com

Figure 3.3 current mirror Integrator.

# 3.4 Lossy current mirror integrator

The lossy current integrator which consists of an nMOS and a pMOS current mirror is shown in figure 3.4. The given circuit can be easily extended to a multi-input and multi-output structure by adding input current sources parallel to Ii and output transistors parallel to M4. The output current is given by  $I_0 = (I_s + I_i)$  where  $I_i$  is the input signal current and it is assumed that (W/L) ratios are equal.

$$T_1(s) = =$$

(3.4)

In the equation (3.4) gm2 and gm4 are respectively the trans-conductance of transistors M2 and M4. The R1 and R3 are respectively the input resistance of transistors M1 and M3. Thus we can realize a lossy current integrators which can be used as a first-order filter section.

Figure 3.4Lossy Current Mirror Integrator.

# International Journal of Advance Research in Science and Engineering Volume No. 08 Ussue No. 07 July 2019

# Volume No.08, Issue No.07, July 2019

# www.ijarse.com

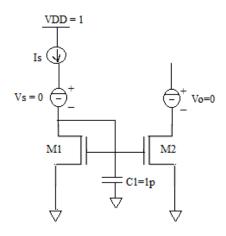

# 3.4 Design of Differentiator using current mirror

Differentiator are almost same in architecture as that of integrator except the interchange in the position of resistor and capacitor. As per the simple RC differentiator circuit, the capacitor is connected in the series of the supply voltage and the resistance is shunt connected in circuit similarly in CM differentiator the capacitor is connected in series with supply current  $I_s$  and the current mirror is connected as given in the figure 3.4, with the assumption that both the transistors in CM having the similar aspect ratios.

Figure 3.4 Differentiator using NMOS Current Mirror.

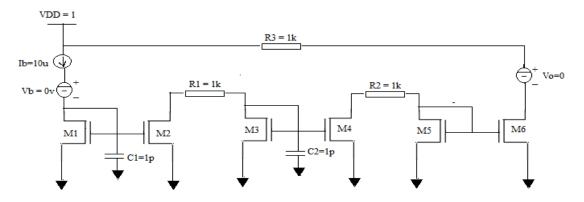

# 3.5 Design of Low Pass Filter

A new topology of low pass filter design is presented here in figure 3.5 with the current mirror Integrator. The circuit is mainly consisting of three blocks first two block is integrator and last block is current amplifier. The circuit architecture is very simple and capable of working at a very low voltage of 1volt. For current amplification scaled current mirror is used, as the whole circuit is made up of only six NMOS transistors and two capacitors therefore, the power dissipation in the circuit is also very small almost negligible. The whole circuit is consisting of two current mirror integrator connected in cascade with a current amplifier at the output terminal and a feedback resistance of value  $1k\Omega$  is also connected.

Figure 3.5Low pass filter using CM Integrator.

ISSN: 2319-8354

The capacitors used in the circuit is of a very low value i.e. 1pF, so the power dissipation throughout the circuit is also very less almost negligible therefore, the above LPF is suitable for low voltage and low power (LVLP) circuits. Similarly, in the same manner high pass filter can be designed using CM differentiator. The higher order filters as well as oscillators can also be designed using CM integrator/differentiator and low pass filter.

### 4. Result and discussion

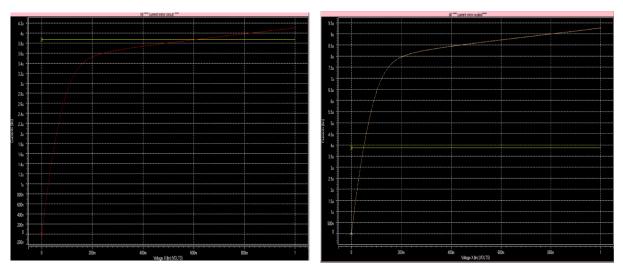

### 4.1 Simulation Results of simple and scaled current mirror

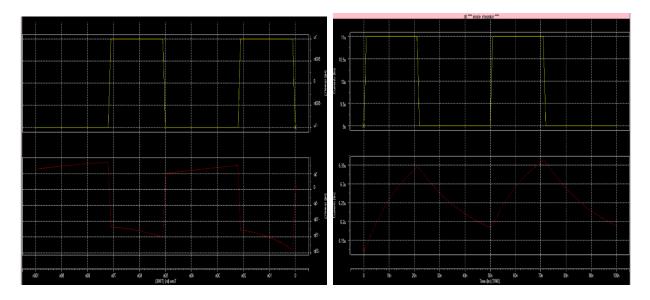

The simulation result of simple NMOS current mirror is as shown in the figure 4.1 (a). The reference current is not exactly  $4\mu A$ . The x-axis is a sweep of the voltage across the current source,  $V_o$  (from 0v to 1v). It can be seen from the graph below at  $V_{DS,sat}$  (=180 mV here)  $M_2$  triodes and the output current,  $I_o$ , goes to zero. The output compliance range for this current source (the range of the output voltages where the current behaves like a current source, that is, not an open or a resistor) is between  $V_{DD}$  and  $V_{DS,sat}$ . The point where  $V_o = V_{DS1} = V_{GS1}$  (at 600mV) is where  $I_o = I_{ref}$  and this condition is important for the matching two currents. Finally, it can be deciphering from the result that  $I_{ref}$  and  $V_{GS1}$  are not dependent on  $V_o$ .

The simulation result scaled NMOS current mirror is shown in the below figure 4.1 (b). The parameter of the  $M_2$  NMOS is scaled by two times in comparison to  $M_1$  transistor hence the output current is the twice of the reference current, this can be seen from the below graph for reference current  $4\mu A$  the output current is  $8\mu A$  on varying the output voltage from 0v to 1v along x-axis .the current values are shown along the y-axis. This circuit can also be used as the current amplifier.

Figure 4.1Plot of (a) simple NMOS Current mirror and (b) Scaled NMOS current mirror in HSPICE Software.

# 4.2 Simulation result of current mirror integrator and lossy integrator

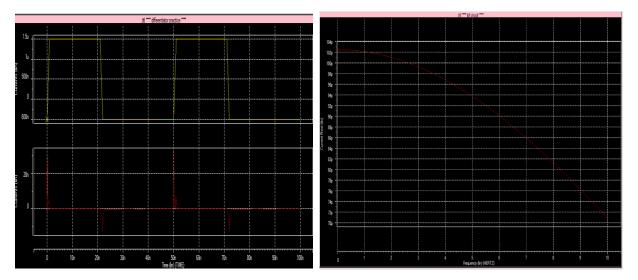

The graph of transient response for square wave of the current mirror integrator shown in the figure 4.2 (a). This graph is between time and the current, the time is taken along the x-axis and the current is taken along the y-axis. The output is taken in between 1ns to 100ns, when input is high the output current rises until the input current is high, which depicts the charging behaviour of the capacitor, and when the input current is low below 0A the output current falls which depicts the discharging behaviour of the capacitor of 1pf value, from the result it is clear that the circuit is behaving like an integrator.

The behaviour of the lossy current mirror integrator circuit is shown in figure 4.2 (b). The graph shows the lossy CM integrator circuit that clearly reflects the perfect behaviour of the integrator, as square wave is taken as the input signal then the output is the perfect triangular wave, which is mathematical integration of the square wave. So, this result clears that for the perfect and practical integration of the signal lossy type integrator circuit is more suitable.

Figure 4.2(a)Behaviour of the CM integrator and (b) Behaviour of the lossy CM integrator.

# 4.3 Simulation result of current mirror differentiator and low pass filter

The result for the transient behaviour of the NMOS current mirror differentiator circuit presented in the fig.4.3 (a), a square wave is applied as input of the differentiator circuit and the corresponding output shows the similar pattern differentiation of original signal is found, the output voltage is zero when the input voltage is constant. The rate of change is zero but as the input changes suddenly from 1.5µA to500nA at t=0, t= 20n, t=50n and so on, there is a maximum change in voltage associated at this instant of time. Therefore, a large output current is produced at the corresponding times where input changes from high to low suddenly. The output current has a positive spice and it is depicted in the output waveform.

Fig. 4.3 (a) Input and output waveform of the differentiator and (b) Low pass filter waveform.

The response of the AC analysis of the low pass filter shown in the Fig. 5.4 is shown below in the Fig. 7.6 and Fig. 7.7. These plots having magnitude on the vertical axis and frequency on the horizontal axis and in fig. 7.7 the horizontal axis has logarithmic scale, in such a way that the physical distance between 0 Hz and 5 Hz is the same as the physical distance between 5 Hz and 10 Hz, and so forth. The general shape of the curve is almost perfectly flat in the passband, and then it begins to drop more rapidly as the input frequency approaches the cut off frequency. This configuration allows to quickly and accurately assess the behaviour of a filter over a very large range of frequencies.

The plot predicts the given circuit passes only the low pass frequencies and blocks the frequencies those are above than the critical frequency. The circuit is given 1v supply in the input terminal for which it is producing the behaviour of the LPF with the cut-off frequency of 72.821 Hz. fig. 7.7 shows the phase shift behaviour of the LPF circuit, the output of the filter lags the input (negative phase shift).

## 5. Conclusion

The growing technology demands for the portable devices operating at low voltage with low power dissipation, urges the need for designing the circuit operating in current mode. In the HSPICE 45nm technology the simulation results are reflected that the results obtained are very similar and identical to the theoretical results and values of the respective conventional circuits. The simple NMOS Current mirror is used for the designing of the different devices for the Analog signal processing like current amplifier, Integrator, Differentiator and low pass filter. The current mirror is the basic building block of the current mode synthesis, so the whole process involved in the circuit operations are solely due to the current flow, as there is no need of the conversion of current into voltage in whole process which generally required in the conventional circuits based op-amp and in

simple RC. There is no voltage loss occurred throughout the circuit designing and in its operation. The designed circuits presented in this study can be said as LVLP circuits.

### 6. Acknowledgement

I am thankful to Integral University, Lucknow, UTTAR PRADESH for providing me research facility.

#### References

- Amanpreet Kaur and Rishikesh Pandey, Current Mode Computational Circuits for Analog Signal Processing, International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering Vol. 3, Issue 4, April 2014.

- 2) D.A Jones and K.W. Martin "Analog integrated circuit design" John Wiley and sons, 2012, 2nd ed.

- 3) R. J. Baker, "CMOS circuit design, layout and simulation" 3rd ed. IEEE press john wiley and sons

- 4) Adel S. Sedra, "Microelectronic circuits, Theory and applications" 5<sup>th</sup> ed. Oxford university press.

- Tamer farouk, Ahmed Nader mohieldin, Ahmed hussain khalil "A low voltage low power CMOS fully differential linear transconductor with mobility reduction compensation" microelectronics journal 43(2012) pg no. 69-76.

- 6) X. Zhu and Y.Son "low distortion low voltage operational transconductance amplifier" IEEE Electronics Letters (Volume: 44, Issue: 25), Dec. 2008.

- Fujihiko matsumoto, Toshio Miyazawa, Shintaro nakamura yashuaki naguchi "Techniques for low voltage low power linear MOS transconductor" IEEE IPSACS 2008

- 8) Hoang Trang, Pham Xuan Hoang ,Trang Hoang quan, "A Novel design of low power, high speed OTA in 50nm- CMOS technology" IEEE ISSPIT 2012.

- 9) Ramon Gonzales Carvajal, Jamie Ramirez angulo, Antonio J. Lopez martin, Antonio Torralba, Juan Antonio Gomez galan, Alfonzo Carlosena, Fernanado Munoz Chavero, "The flipped voltage follower: A useful cell for low voltage low power circuit design" IEEE trans. On circuit and system-I regular papers, Vol.2, No.57, 2005.