# SECURITY SYSTEM BASED ON VOICE SENSORS

# Ilham Ahmad Quraishi<sup>1</sup>, Ali Abbas Rizvi<sup>2</sup>, Sandeep Jindal<sup>3</sup>, Amit Kumar<sup>4</sup>

Electronics and Communication Engineering, Accurate Institute of Mgmt and Tech(GBTU),(India)

#### **ABSTRACT**

As our project we are going to present "Power Line Communication". Our project mainly used for telecommunication Tele-protection and Tele-monitoring between electrical substations through power lines at high voltages, such as 110kV, 220kV, 400kV. In a PLCC system the communication is established through the power line.

Keywords: LCD, ASCII, PLCC system.

#### **I INTRODUCTION**

Power line communication (PLC) is a technique transmitting voice or data at a rapid speed through a power line in a house, an office, a building, and a factory, etc. Power-line communication systems have become increasingly viewed employed as an attractive alternative to conventional hard-wired communication systems, which require dedicated communication wiring, and wireless systems, which involve complex and costly transmitter and receiver circuits. In power line communication, the existing alternating current (AC) power wires serve as a transmission medium by which information is relayed from a transmitter or control station to one or more receivers or loads connected downstream from an AC source. There is a significant advantage to the use of alternating current (AC) power lines for purpose of communication between electronic devices using a power line communication system. Since no new wires are required to implement the function of communication, power-line communication systems greatly reduce the complexity and effort of installation, particularly in building retrofit applications in which it is highly desirable to be able to install an energy control system with little or no alteration of the existing electrical wiring.

## II CONSTRUCTION

The components used are:

- IC UM9121B

- IC CM8870

- IC 74154

- IC 7805 Power Regulator

- IC 741 Op. Amplifier

- IC 7447 Seven Segment Display

- Resistors

- Capacitors

- Relay

- Diode

- LED

- Keypad

Laser Torch

• Speaker 0.5W

Transformer

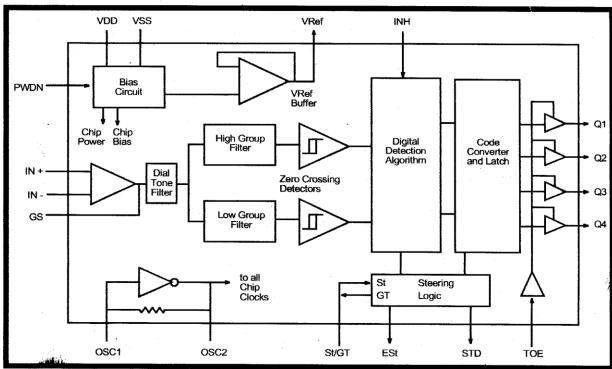

## III BLOCK DIAGRAM

Figure 1 - Functional Block Diagram

## IV CIRCUIT DIAGRAM

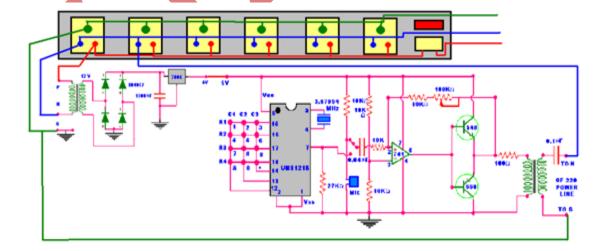

## 4.1 Transmitter Section

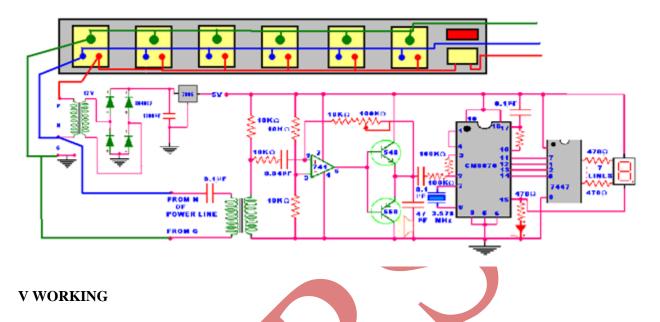

#### 4.2 Receiver Section

In a PLCC system the communication is established through the power line. The audio frequency is carried by a carrier frequency and the range of carrier frequency is from 50kHz to 500kHz. The modulation generally used in this system is amplitude modulation. The carrier frequency range is allocated to include the audio signal, protection and the pilot frequency. The pilot frequency is a signal in the audio range that is transmitted continuously for failure detection. The voice signal is converted/compressed into the 300Hz to 4000Hz range, and this audio frequency is mixed with the carrier frequency. The carrier frequency is again filtered, amplified and transmitted. The transmission of these HF carrier frequencies will be in the range of 0 to +32db. This range is set according to the distance between substations. The powerline communication technology utilizes a power line as a signal transmission channel. This technology makes it possible to perform communication between a plurality of communication devices by connecting each of those devices to a receptacle installed in each room in a house. Use of existing power lines as a communication medium eliminates installation costs for adding dedicated communication wiring to existing structures. Such a power line communication system can be used for monitoring and controlling basic function including energy management, security, and safety control in applications including homes, factories, offices, automobiles and aircraft. Electric utility companies utilize power line communication systems to provide a means for a central station to communicate command signals to remote receivers which are located at the sites of electric energy consumers.

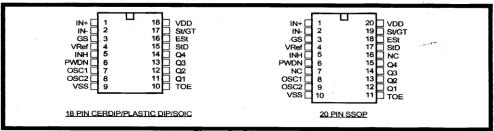

## VI PIN DESCRIPTION

## MT8870D/MT8870D-1 ISO2-CMOS

Figure 2 - Pin Connections

#### Pin Description

| Pin#      |            |                  |                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18        | 20         | Name             | Description                                                                                                                                                                                                                                                                                                                                                                                 |

| 1         | 1          | IN+              | Non-Inverting Op-Amp (Input).                                                                                                                                                                                                                                                                                                                                                               |

| 2,        | 2          | IN-              | Inverting Op-Amp (Input).                                                                                                                                                                                                                                                                                                                                                                   |

| 3         | 3          | GS               | Gain Select. Gives access to output of front end differential amplifier for connection of feedback resistor.                                                                                                                                                                                                                                                                                |

| 4 -       | 4          | V <sub>Ref</sub> | Reference Voltage (Output). Nominally $V_{DD}/2$ is used to bias inputs at mid-rail (see Fig. 6 and Fig. 10).                                                                                                                                                                                                                                                                               |

| 5         | 5          | INH              | Inhibit (Input). Logic high inhibits the detection of tones representing characters A, B, C and D. This pin input is internally pulled down.                                                                                                                                                                                                                                                |

| 6         | 6          | PWDN             | <b>Power Down (Input).</b> Active high. Powers down the device and inhibits the oscillator. This pin input is internally pulled down.                                                                                                                                                                                                                                                       |

| 7         | 8          | OSC1             | Clock (Input).                                                                                                                                                                                                                                                                                                                                                                              |

| , 8       | 9          | OSC2             | Clock (Output). A 3.579545 MHz crystal connected between pins OSC1 and OSC2 completes the internal oscillator circuit.                                                                                                                                                                                                                                                                      |

| 9         | 10         | V <sub>SS</sub>  | Ground (Input). 0V typical.                                                                                                                                                                                                                                                                                                                                                                 |

| 10        | 11<br>:: 3 | TOE              | Three State Output Enable (Input). Logic high enables the outputs Q1-Q4. This pin is pulled up internally.                                                                                                                                                                                                                                                                                  |

| 11-<br>14 | 12-<br>15  | Q1-Q4            | Three State Data (Output). When enabled by TOE, provide the code corresponding to the last valid tone-pair received (see Table 1). When TOE is logic low, the data outputs are high impedance.                                                                                                                                                                                              |

| 15        | 17         | StD              | <b>Delayed Steering (Output).</b> Presents a logic high when a received tone-pair has been registered and the output latch updated; returns to logic low when the voltage on St/GT falls below V <sub>TSt</sub> .                                                                                                                                                                           |

| 16        | 18         | ESt              | Early Steering (Output). Presents a logic high once the digital algorithm has detected a valid tone pair (signal condition). Any momentary loss of signal condition will cause ESt to return to a logic low.                                                                                                                                                                                |

| 17        | 19         | St/GT            | <b>Steering Input/Guard time (Output) Bidirectional.</b> A voltage greater than $V_{TSt}$ detected at St causes the device to register the detected tone pair and update the output latch. A voltage less than $V_{TSt}$ frees the device to accept a new tone pair. The GT output acts to reset the external steering time-constant; its state is a function of ESt and the voltage on St. |

| 18        | 20         | $V_{DD}$         | Positive power supply (Input). +5V typical.                                                                                                                                                                                                                                                                                                                                                 |

|           | 7,<br>16   | NC               | No Connection.                                                                                                                                                                                                                                                                                                                                                                              |

The LCD interface is a parallel bus, allowing simple and fast reading/writing of data to and from the LCD. This waveform will write an ASCII Byte out to the LCD's screen. The ASCII code to be displayed is eight bits long and is sent to the LCD either four or eight bits at a time. If four bit mode is used, two "nibbles" of data (Sent high four bits and then low four bits with an "E" Clock pulse with each nibble) are sent to make up a full eight bit transfer. The "E" Clock is used to initiate the data transfer within the LCD.

Sending parallel data as either four or eight bits are the two primary modes of operation. While there are secondary considerations and modes, deciding how to send the data to the LCD is most critical decision to be made for an LCD interface application. Eight bit mode is best used when speed is required in an application and at least ten I/O pins are available. Four bit mode requires a minimum of six bits. The "R/S" bit is used to select whether data or an instruction is being transferred LCD. If the Bit is set, then the byte at the current LCD "Cursor" Position can be read or written. When the Bit is reset, either an instruction is being sent to the LCD or the execution status of the last instruction is read back (whether or not it has completed). The different instructions available for use with the 44780 are shown in the table below:

### VII CONCLUSION

We have presented "Power line Communication" as our project. Our Project mainly used for telecommunication Tele-protection and Tele-monitoring between electrical substations through power lines at high voltages, such as 110kV, 220kV, 400kV. In a PLCC system the communication is established through the power line.

### **REFERENCES**

- [1] www.atmel.com

- [2] www.beyondlogic.org

- [3] www.dallassemiconductors.com

- [4] www.maxim-ic.com

- [5] www.alldatasheets.com

- [6] www.howstuffworks.com

- [7] www.digi.com

- [8] www.wikipedia.org